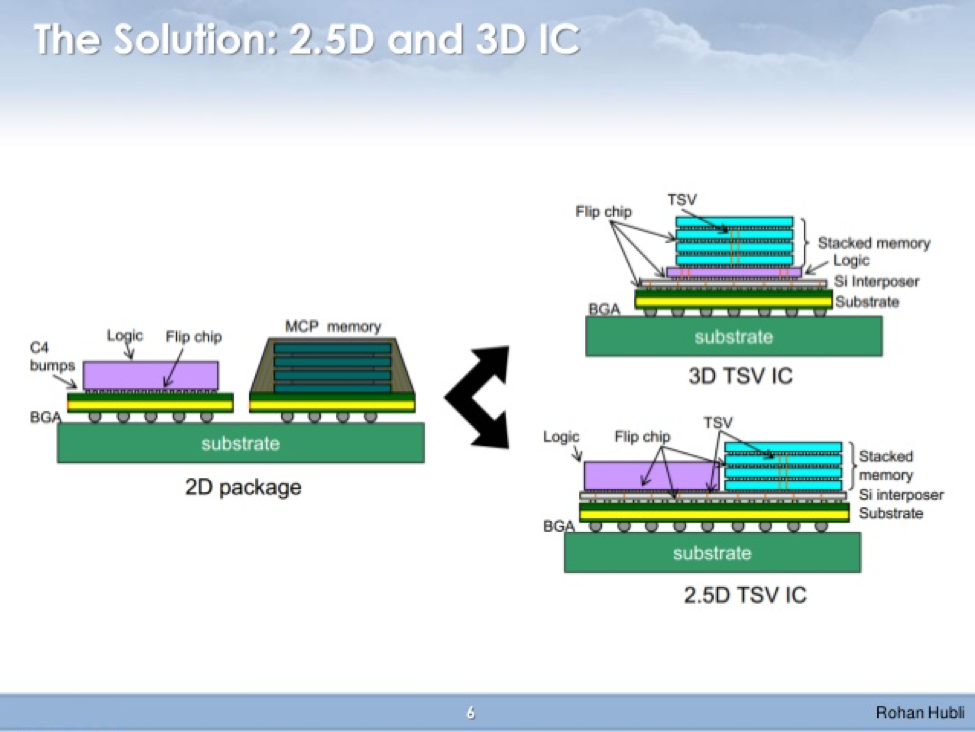

IFTLE 485 TSMC, Samsung and Sony Showcase Advanced Packaging at 21 IEEE ISSCC Finishing up our look at the 21 IEEE ISSCC, Forum 5 was entitled Enabling New System Architectures with 25D, 3D, and Chiplets This was another clear example of a heretofore frontend conference now focusing on advanced packaging technologies10 25/3D PACKAGING TRENDS Stack packaging—more than Moore's Law—has now been widely implemented for use to increase the capabilities of commercial electronics because of increasing cost and limitation of die fabrication with finer features 1–3 Moore's Law, stating that the number of transistors on a given chip will double every two Illustration of a 25/3D packaging Model of AMD Fury X chipset The ComputerAided Design ("CAD") files and all associated content posted to this website are created, uploaded, managed and owned by third party users

What Is 3d Integration 3d Incites

2.5 3d packaging

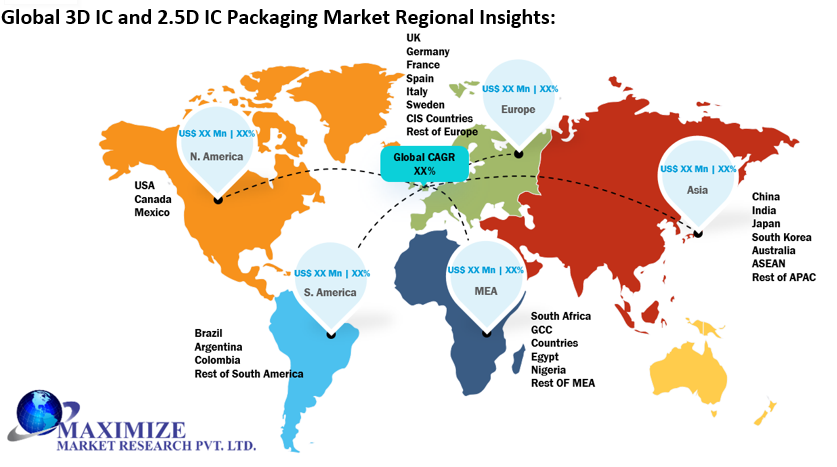

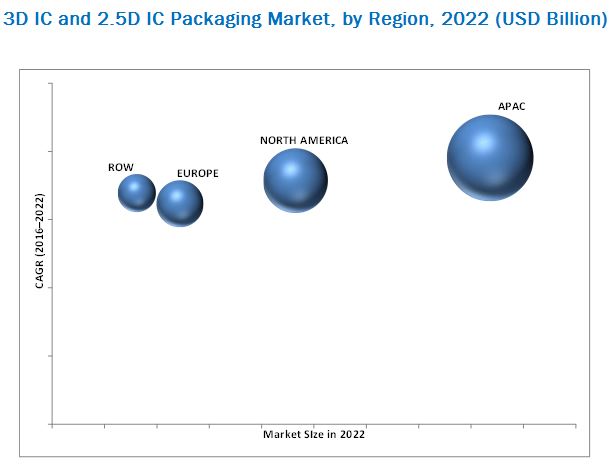

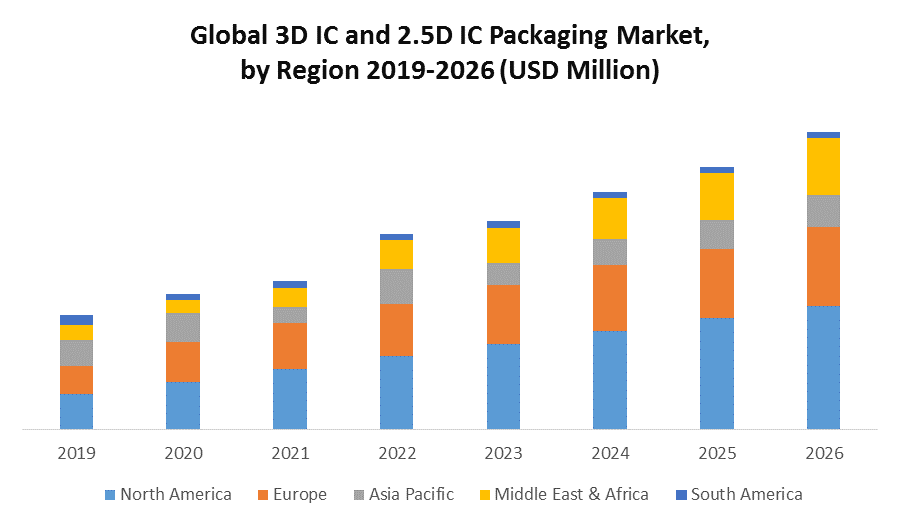

2.5 3d packaging-The 3D IC and 25D IC Packaging market in the US is estimated at US$26 Billion in the year China, the world`s second largest economy, is forecast to reach a projected market size of US$1241 Billion by the year 27 trailing a CAGR of 346% over the analysis period to 27Buy Crucial BX500 2TB 3D NAND SATA 25Inch Internal SSD, up to 540MB/s CT00BX500SSD1 & BX500 1TB 3D NAND SATA 25Inch Internal SSD, up to 540MB/s CT1000BX500SSD1 Internal Solid State Drives Amazoncom FREE

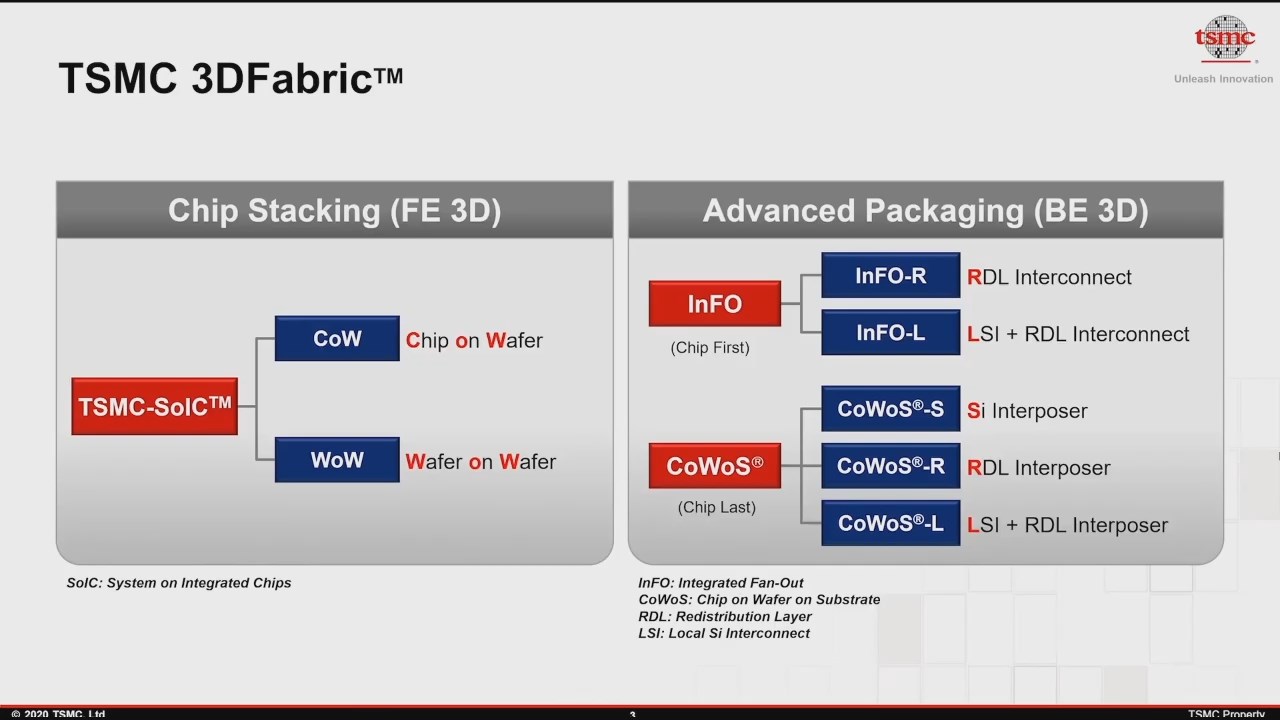

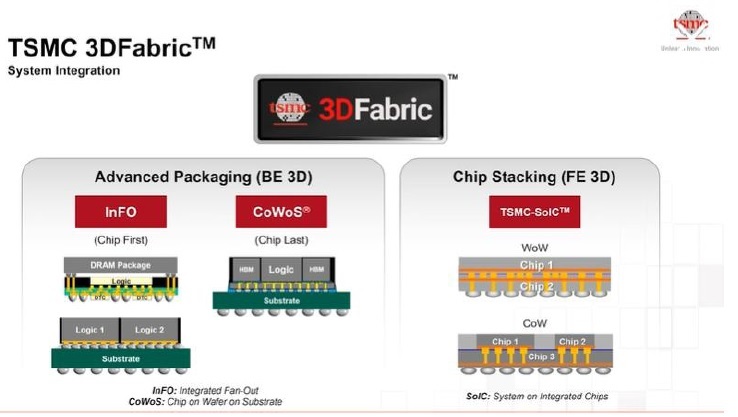

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Use the model to for your product Include supplier specific details and incoming die preparation in your analysis View the detailed costs—including labor, material, capital, tooling, and yield impacts—for every step Labor rate Lot size Overhead rate The market has been segmented on the basis of packaging technology into 2D, 25D, and 3D IC Based on package type, the system in package market has been classified into ball grid array, surface Samsung Foundry Certifies Cadence System Analysis and Advanced Packaging Design Tool Flow for 25/3D Chip Designs Proven flow featuring the Celsius Thermal Solver and Clarity 3D Solver accelerates 25/3D designs for hyperscale, communications and

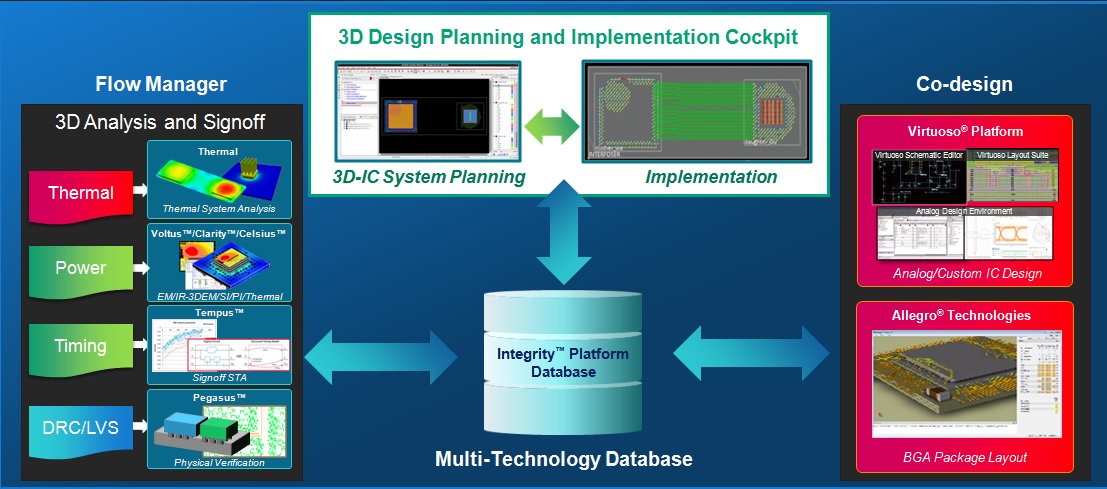

Synopsys introduced its 3DIC Compiler platform to transform the design and integration of complex 25 and 3D multidie system in a package It provides an unprecedented fully integrated, highperformance, and easytouse environment, offering architectural exploration, design, implementation, and signoff with signal, power, and thermal integrity optimizations, all in25/3d ic Artificial intelligence, high speed networking, and other processing intensive devises are moving to 25 and 3D package structures to achieve high memory bandwidth and line data rates Vertical integration compels manufacturers to use transmissive techniques to monitor their processes however conventional point projection highCrucial MX500 1TB 3D NAND SATA 25 Inch Internal SSD, up to 560MB/s CT1000MX500SSD1 & MX500 500GB 3D NAND SATA 25 Inch Internal SSD, up to 560MB/s CT500MX500SSD1 Capacity250GB Product PackagingFrustrationFree Packaging Start your system in seconds, store up to 2TB of data, and upgrade with an SSD you can count on Join more and

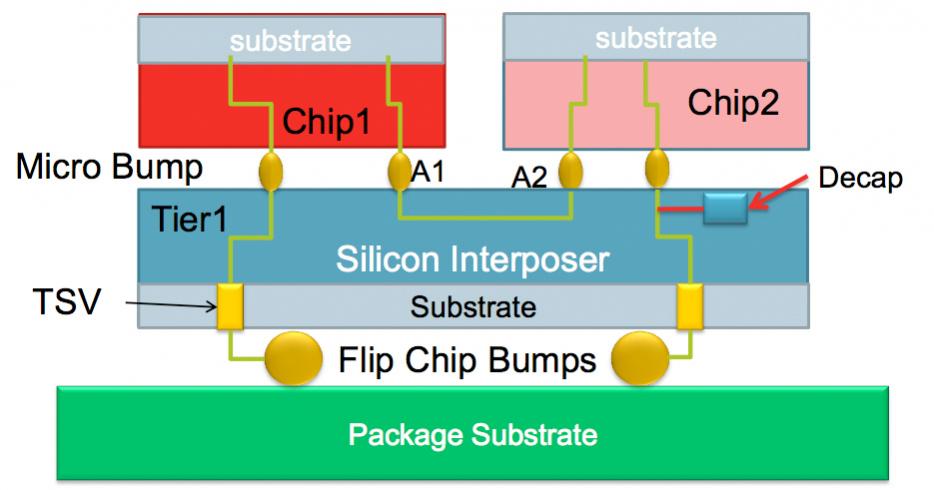

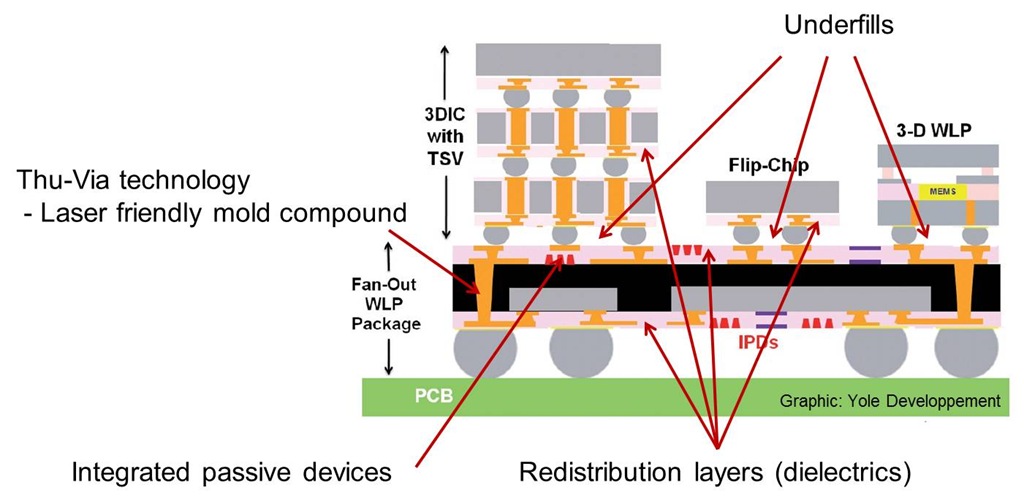

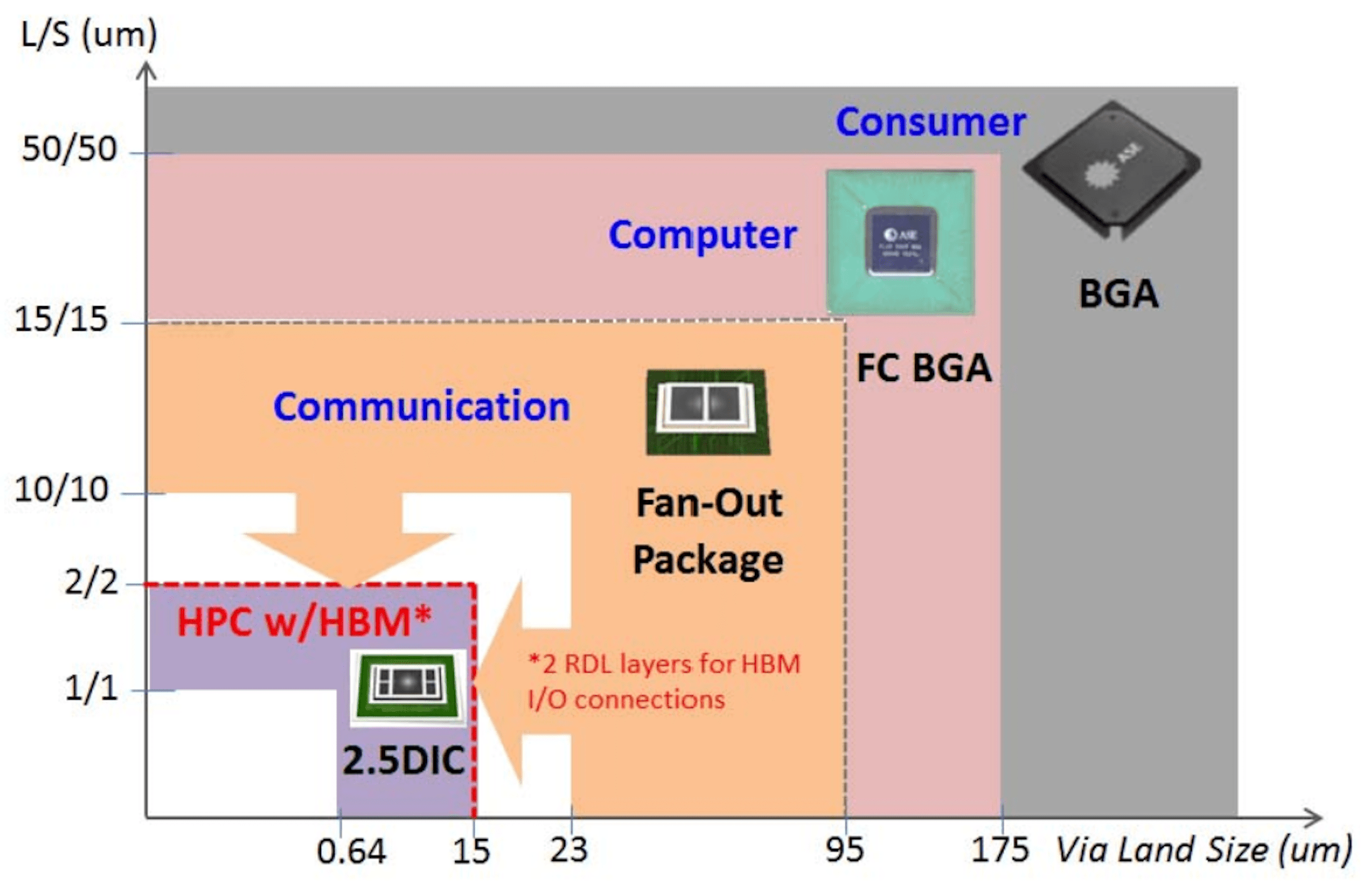

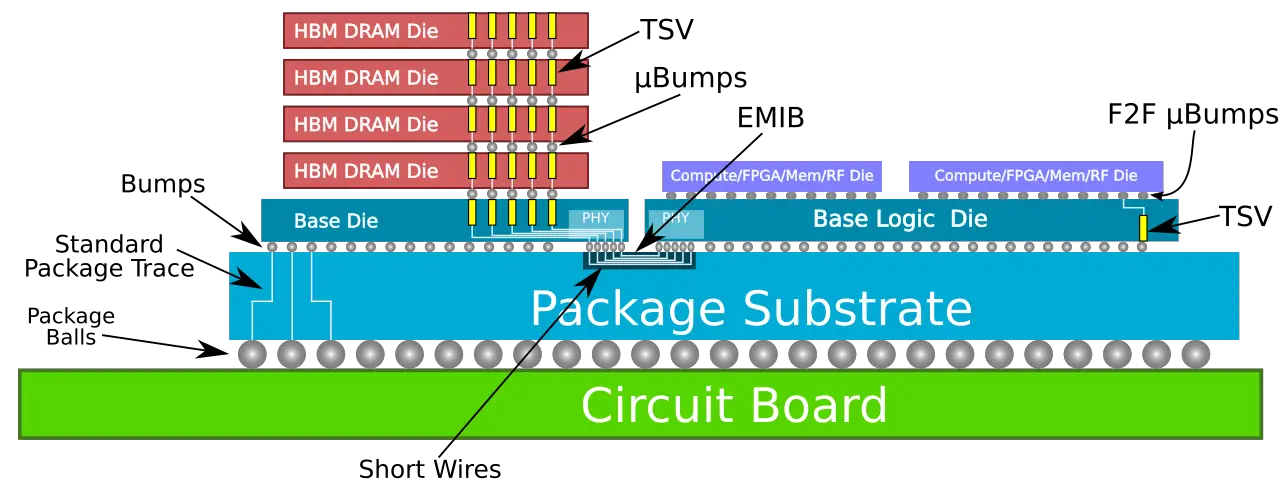

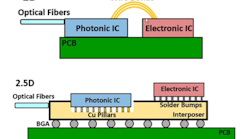

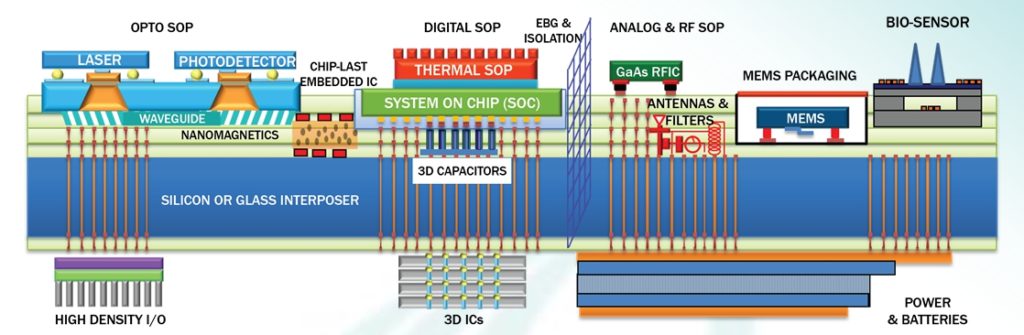

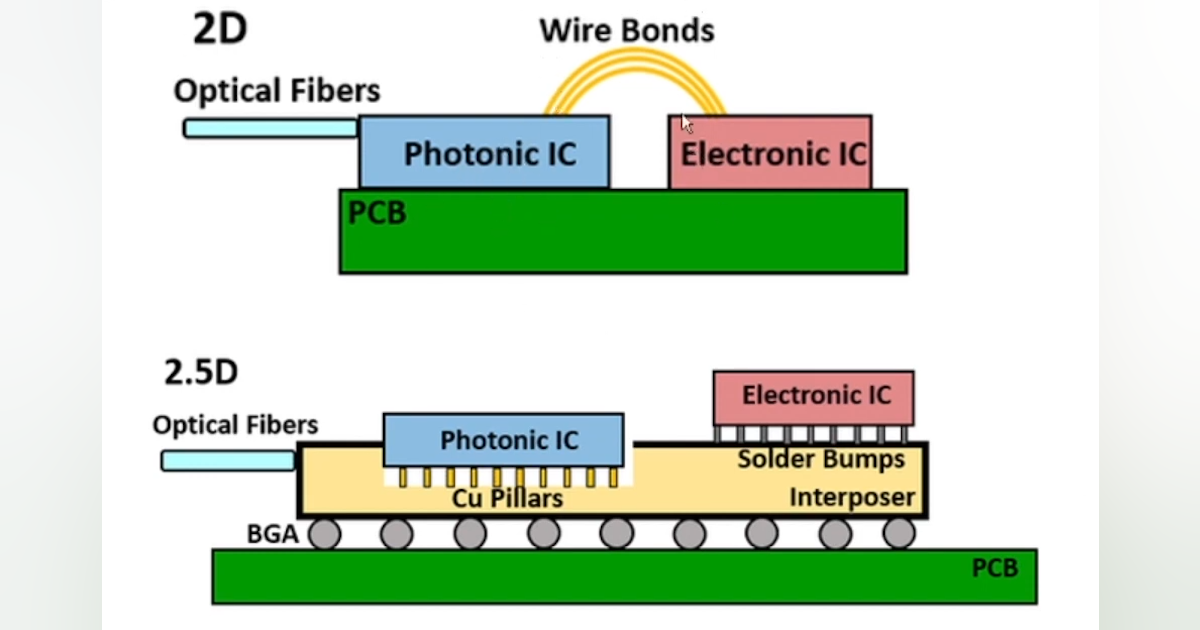

Blogs, Packaging IFTLE By Phil Garrou advanced packaging Let's look at a few more presentations from the SEMI 3D & Systems Summit which was held in late January in Dresden KLA showed this interesting schematic of where inspection was necessary for highdensity 25/3D packagingSelect a packaging style, quantity, and choose from custom or stock sizes – then start designing your custom boxes Add customization options like images, text, and any color your brand requires As you design you'll see an instant quote so you know exactly what your final order will come to Get started now Tiny minimums25D is a packaging methodology for including multiple die inside the same package The approach typically has been used for applications where performance and low power are critical Communication between chips is accomplished using either a silicon or organic interposer, typically a chip or layer with throughsilicon vias for communication While communication between chips

The Race To Next Gen 2 5d 3d Packages

2

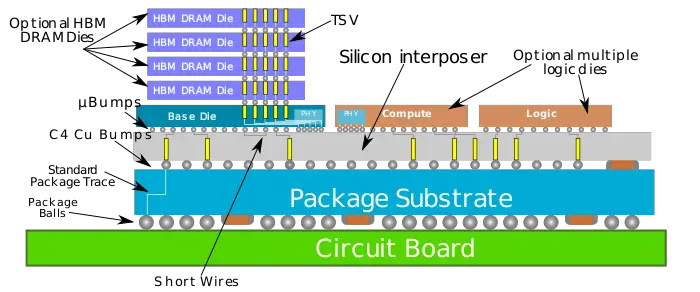

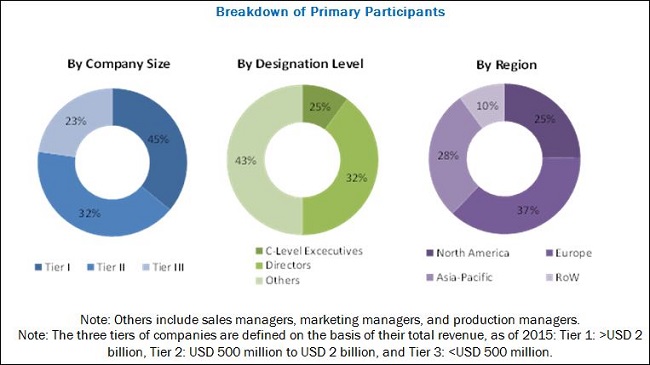

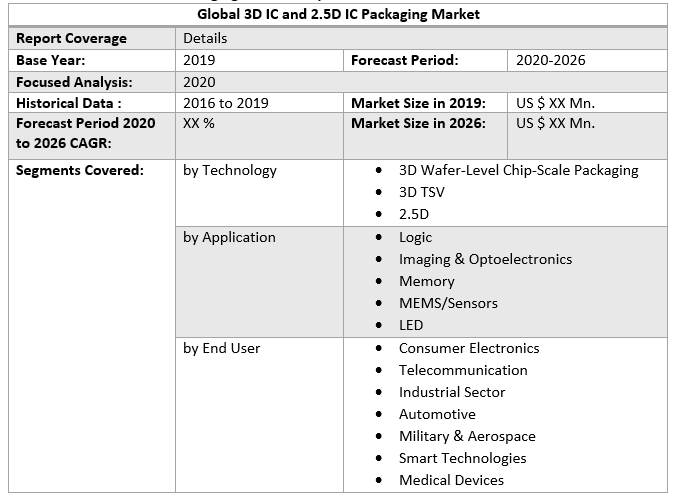

Fig 1, which shows a modern 25D test vehicle including packaging technologies such as silicon interposer and micropillar interconnects 3 Figure 1 shows two fullwaferthickness dice, which are stacked on a thinned silicon interposer The dice package is Opportunities for 25/3D Heterogeneous SoC Integration Abstract As the design complexity grows dramatically in modern circuit designs, 25D/3D chip/package/board integration has become effective for optimizing system performance and power consumption Various 25D/3D technologies have been explored Global 3D IC and 25D IC Packaging Market size was valued at US$ XX Mn in 19 and the total revenue is expected to grow at XX% through to 26, reaching nearly US$ XX Mn The global 3D IC and 25D IC Packaging market report is a comprehensive analysis of the industry, market, and key players

2 5d Semiconductor Engineering

3d Ic And 2 5 D Ic Packaging Industries In Depth Analysis

Power & Signal integrity prototyping in system technology cooptimization (STCO) High Density Advanced Packaging (HDAP) using chiplets & 3D packaging Home page Using a System Technology CoOptimization (STCO) approach for 25/3DASE is one of the pioneers in 25D/3D packaging technology and has successfully introduced the mass production of the world's first 25D IC package equipped with High Bandwidth Memory (HBM) 25D refers to die stacking package using interposers to achieve the best performance of internet connectivity Summary The growing adoption of 25D/3D package technologies offers unique "More than Moore" opportunities for PPA/V and costoptimized system implementations Early 25D/3D designs used disjoint tool flows, within limited system planning exploration options A unified platform, flow manager and model database are needed to provide users

Jcet Group 2 5d 3d Integration

2 5d And 3d Designs Semiwiki

25D/3D packaging I've spent most of my career in the ASIC business In 03, Gartner predicted the ASIC market would grow to $169B During that time, there were a number of startups building ASICs, but the applications were a bit specialized and aimed at new marketsChip Packaging Part 4 25D and 3D Packaging Dr Navid Asadi's group examines 25D and 3D packaging for expanding capabilities and capacities of chip solutions Peter Xi25D & 3D Packaging Cost Model Which applications are right for this technology?

Design Planning And Optimization For 3d And 2 5d Packaging Semiwiki

What Is 3d Integration 3d Incites

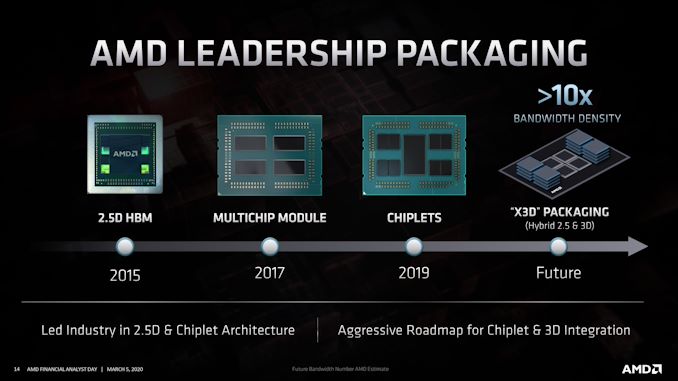

AMD GPU VEGA Product 25D/3D Package with HBM2 • AMD GPU Vera Package Supply Chain • GLOBALFOUNDRIES GPU and interposer • ASE Assembly • Samsung HBM2 • IBIDEN laminate subtrate TSV inside HBM and Silicon Interposer • 3D TSV and 25 packagingAutomated verification of 25/3D IC latchup prevention With the Calibre PERC reliability platform, an automated 25/3D IC latchup prevention verification methodology is available that addresses the multiple challenges inherent in advanced latchup protection for multidie packagesDavid Schor 25D packaging, 3D packaging, CoEMIB, EMIB, Foveros, Intel A look at ODI, a new family of packaging interconnect technologies that bridges the gap between Intel's EMIB (25D) and Foveros (3D) by providing the flexibility of an EMIB in 3D with additional benefits of thermal & power Read more

2 5d 3d Ase Group

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

2D vs 25D vs 3D ICs 101 By Max Maxfield 6 I see a lot of articles bouncing around the Internet these days about 25D and 3D ICs One really good one that came out recently was 25D ICs are more than a stepping stone to 3D ICs by Mike Santarini of Xilinx On the other hand, there are a lot of other articles that have "3D ICsThrough Silicon Via (TSV) interconnects have emerged to serve a wide range of 25D TSV and 3D TSV packaging applications and architectures that demand very high performance and functionality at the lowest energy/performance metric To enable the use of TSVs in 25D/3D TSV architectures, we have developed several backend technology platforms to 25/3D Level Heterogeneous Integration • Heterogeneous Integration • In the context of describing 25D/3D packaging level of technology • Integrating dissimilar chips using a packaging technology with I/O density higher than organic substrate (Feature size smaller than organic substrate, or 3D die) • Technology drivers • High bandwidth

3d Ic And 2 5d Ic Packaging Global Market Trajectory Analytics

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

Adopters of silicon and glass based interposer fabrication The material presented will also reference 3D packaging standards and recognize innovative technologies from a number of industry sources, roadmaps and market forecasts Key words 25D, 3D Semiconductor Package Technology, Through Silicon Via, TSV, Through Glass Via, TGV Introduction The overall IC packaging market is projected to reach $68 billion in 19, up 35% over 18, according to Yole Développement Of those figures, advanced packaging is projected to grow at 43% in 19, compared to 28% for traditional/commodity packaging, according to Yole More 25D/3D and chiplets IC packaging is important for several reasons Without the benefit of volume production, the cost of 25D and 3D packaging could stay high for a long time In this paper, we will provide cost model results of a complete 25D and 3D manufacturing process Each manufacturing activity will be included and the key cost drivers will be analyzed regarding future cost reductions

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging Optoelectronics Memory Mems Sensors Led Power Packaging Technology 3d Wafer Level Chip Scale Packaging 3d Tsv 2 5d End User Industry And Region Global

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

IC Packaging Design & Verification Monolithic scaling limitations are driving the growth of 25/3D multidie heterogeneous and homogeneous integrated technologies allowing PPA targets to be met Our integrated flow addresses the challenges of prototyping to Signoff for FOWLP, 25/3D IC, and other emerging technologies View Products 25/3D IC Packaging Technologies Part 1 Overview IEEE/CPMT, Herb Reiter eda2asic Consulting IncHerb Reiter, eda2asic Consulting, Inc herb@eda2asiccom 1 eda2asic AGENDA Part 1 Introduction eda2asic EndUseMarkets for 25/3DGlobal 3D Semiconductor Packaging Market Overview Global 3D semiconductor packaging market size is estimated to reach $ billion by 22, growing at a CAGR of 157 % from 16 to 22 3D semiconductor packaging refers to an advanced packaging technology of semiconductor chips in which two or more layers of active electronic components are stacked

Eng Sub 2 5d Package Technology Gpu Hbm Amd Nvidia Tsmc Youtube

Global 3d Ic And 2 5d Ic Packaging Market 17 Taiwan

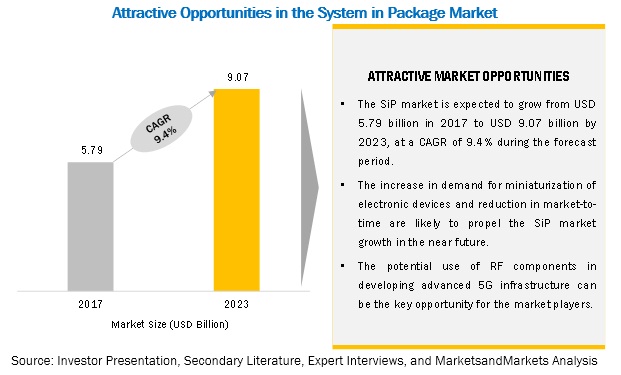

Together with 25D/3D packaging this extends Moore's Law at systemlevel Times have changed The industry is seeking alternatives to design and manufacture the latest Systems on Chips (SoCs) using System in Package (SiP) and chipletbased approaches by leveraging HighEnd Packaging to mix both the latest and mature nodes 25D/3D packagingA 25D integrated circuit (25D IC) combines multiple integrated circuit dies in a single package without stacking them into a threedimensional integrated circuit (3DIC) with throughsilicon vias (TSVs) The term "25D" originated when 3DICs with This study explored Through Glass Via (TGV) Formation Technology by using Focused Electrical Discharging Method for alkalifee glass which has well matched CTE with Si 25D/3D Packaging has presently attracted lots of attention, an interposer is recognized as one of key materials, and its development of new fine pitch, high dense, and low cost interposer are

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

2 5d 3d Packaging Applications Indium Corporation

25D & 3D Packaging Indium Corporation is a world leader in the design, formulation, manufacture and supply of semiconductorgrade fluxes and associated materials, enabling 25 and 3D assembly processes, as well as more standard flipchip assembly 1325D/3D TSV & Wafer Level Integration Technology & Market updates 19 Sample wwwyolefr ©19 In this report ADVANCED PACKAGING PLATFORMS Focus on 3D stacking packaging platforms in this report No substrate FanOut WLCSP Organic substrates Wirebond BGA CSP COB BOC WB CSP LGA FlipChip BGA FC BGA FO on Substrate 25/21D 3D*Working in three dimensions (3D) means that you have the ability to control at least three axes simultaneously 3D contouring can then be accomplished by creating curves that use all three axes at once, like in a helical cut You will most often need a full CAM program to create gcode files capable of performing 3D contouring

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

2 5d 3d Packaging Pradeep S Techpoints

Huemoeller , " Market Demand Readiness for 2 5 / 3 D TSV Products " IMAPS 12 Device Packaging Conference , Scottsdale , AZ March 5 12 2 S Arkalgud , " 2 5 and 3 DThe First Wave of 3D ICs Perfecting the 3D chip R Colin Johnson 1031 AM EDT You've heard the hype The foundation of semiconductor fabrication will be transformed over the next few years as The Xilinx 25D Supply Chain Package Substrate 28nm FPGA & InterposerXpedition IC Packaging Design tools provide a complete design solution for creating complex, multidie homogeneous or heterogeneous devices using FOWLP, 25/3D, or systeminpackage (SiP) modules, as well as IC package assembly prototyping, planning, codesign, and substrate layout implementation

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

Pin On Telecharger Gratuit

25/3D wafer level packaging is one of the important key technologies in advanced microelectronic packaging and system integration worldwide This concept has specific advantages in terms of heterogeneous integration of multiple devices such as sensors, processors, memory ICs and transceivers with excellent electrical performance and small form factor

High End Packaging Intel And Tsmc Are Competing What Will Be The Strategy Of Samsung And The Others I Micronews

Denmark 3d Ic 2 5d Ic Packaging Market

3d Ic And 2 5d Ic Packaging Global Market Trajectory Analytics

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

2 5d Vs

2 5d 3d Ase Group

Advanced Packaging Strong Momentum Driven By Tsmc Intel And Samsung Ee Times Asia

2

3d Ic 2 5d Ic Packaging Market Report Global Forecast To 28

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Polymer Challenges In Electronic Packaging Overview Polymer Innovation Blog

Chip On Wafer On Substrate Cowos Tsmc Wikichip

Three Dimensional Integrated Circuit Wikipedia

Yole Developpement 3d Packaging Free Webcast On May 27 Yole Dev System Plus Consulting Join Forces To Share Their Expertise On The 2 5d 3d Packaging We Will Also

2

2 5d Packaging Vs 3d Packaging Anny Zhang Indium Corporation Blogs Chip Attach Gold Solder Indium Indium Corporation

1

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

The Next Advanced Packages

Advanced Packaging Strong Momentum Driven By Tsmc Intel And Samsung Ee Times Asia

Iftle 1 Imaps Device Packaging Conf Part 2 Amd Scp Insights From Leading Edge

Amd Discloses Its Multi Layer Chiplet Design Era Starting With Zen 3 With 3d Stacked V Cache Technology

Lost In The Advanced Ic Packaging Labyrinth Know These 10 Basic Terms Edn

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

2 5d 3d Ase Group

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Southeast Asia Ems And Printed Circuit Boards Assembly News

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

About 2 5d Technology Nhanced Semiconductors Inc

Webinar Design Methodologies For Next Generation Heterogeneously Integrated 2 5 3d Ic Designs Semiwiki

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

Different 3d Technologies Arranged According To Manufacturing Costs And Download Scientific Diagram

3d Ic And 2 5d Ic Packaging Market In Depth Analysis Taiwan

2 5d 3d Packaging Applications Indium Corporation

2

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

Advanced Packaging Market To Grow 8 To 26 10 07 Packaging Strategies

Advanced Packaging Five Trends To Watch In 17 Electronic Products

More 2 5d 3d Fan Out Packages Ahead

2 5d 3d Ase Group

3d Ic And 2 5d Ic Packaging Market Size Share Trends Analysis Industry Report 24 Igr

2

Increased Funds Could Catalyze Tsmc S 3d Ic Research News

Packaging Wars Begin

Chip Packaging Part 4 2 5d And 3d Packaging Electronic Design

Confusion Grows Over Packaging And Scaling

Packaing Part 4 2 5d And 3d Youtube

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Figure 1 From 2 5d 3d Tsv Processes Development And Assembly Packaging Technology Semantic Scholar

Left Right Above And Under Intel 3d Packaging Tech Gains Omnidirectionality Wikichip Fuse

2 5 3d Packaging Path Finding 3d Incites

Eetimes 3d Ic Design

Amd Discusses X3d Die Stacking And Packaging For Future Products Hybrid 2 5d And 3d

System In Package Market By Packaging Technology Package Packaging Method Device Application Covid 19 Impact Analysis Marketsandmarkets

3d Thursday 28nm Design And 2 5d Packaging Saves Xilinx A Ton Of Power You Can Too Even If You Re Not Designing Fpgas Eda360 Insider

2

High End Performance Packaging 3d 2 5d Integration I Micronews

Semiconductor Packaging 2 5d 3d And Beyond High Technology Business Development Ira Feldman

2

2 5d 3d Packaging Applications Indium Corporation

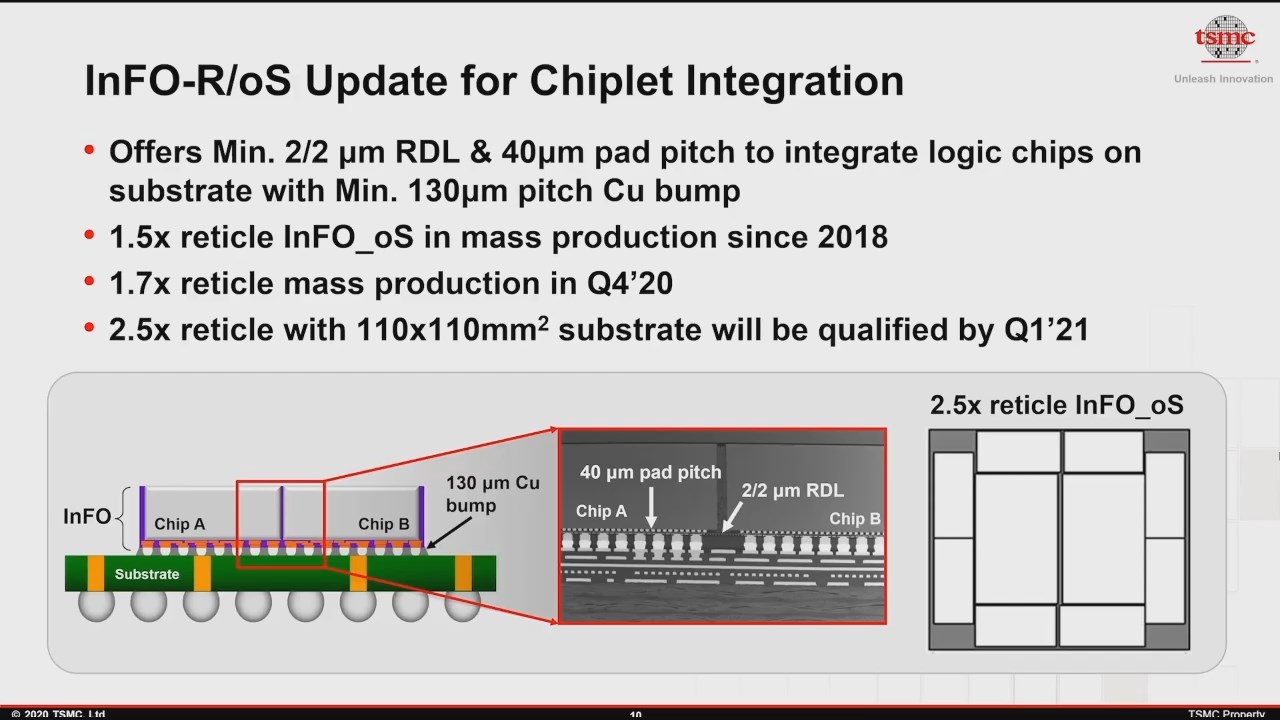

Highlights Of The Tsmc Technology Symposium 21 Packaging Semiwiki

Sorting Out Packaging Options

Design Electrical Mechanical Thermal Prc Gatech Edu Georgia Institute Of Technology Atlanta Ga

About 2 5d Technology Nhanced Semiconductors Inc

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

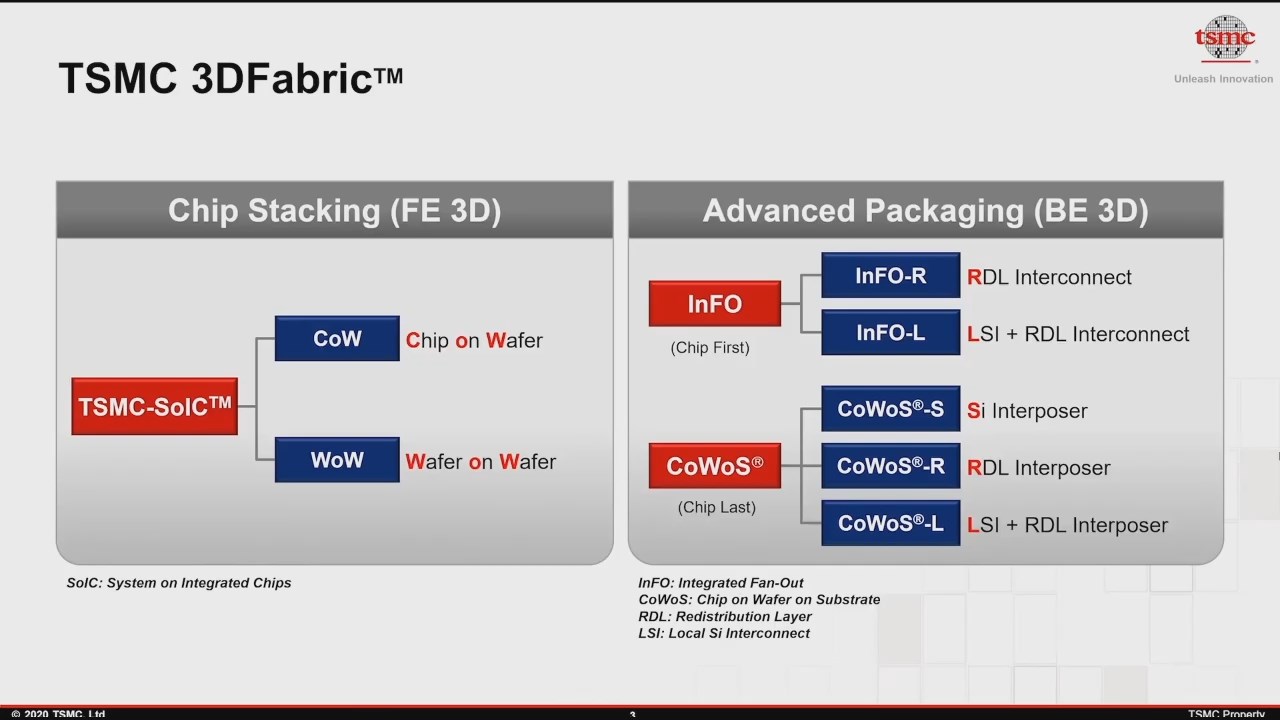

Introducing Tsmc 3dfabric Tsmc S Family Of 3d Silicon Stacking Advanced Packaging Technologies And Services Taiwan Semiconductor Manufacturing Company Limited

Advanced Packaging Osats Foundries And Idms Part Of The Game

Automated Latch Up Verification In 2 5d 3d Ics In Compliance Magazine

High End Performance Packaging 3d 2 5d Integration I Micronews

Toward 2 5 3d Packaging Enablement Through Copper Pillar

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

Chip Packaging Part 4 2 5d And 3d Packaging Electronic Design

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

1

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

2d Vs 2 5d Games

17 European 3d Summit Making Advanced Packaging Great Again

Packaing Part 4 2 5d And 3d Youtube

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

High End Performance Packaging 3d 2 5d Integration I Micronews

0 件のコメント:

コメントを投稿